# LASER INTERFEROMETER GRAVITATIONAL WAVE OBSERVATORY LIGO Laboratory / LIGO Scientific Collaboration

LIGO-T2500372-v1 Advanced LIGO 4 November 2025

Fast Digital Servo: Timing Diagrams

Daniel Sigg

Distribution of this document: LIGO Scientific Collaboration

This is an internal working note of the LIGO Laboratory.

California Institute of Technology LIGO Project – MS 18-34 1200 E. California Blvd. Pasadena, CA 91125

Phone (626) 395-2129 Fax (626) 304-9834 E-mail: info@ligo.caltech.edu

P.O. Box 1970

Richland WA 99352

Phone 509-372-8106

Fax 509-372-8137

Massachusetts Institute of Technology LIGO Project – NW22-295 185 Albany St Cambridge, MA 02139 Phone (617) 253-4824 Fax (617) 253-7014 E-mail: info@ligo.mit.edu

P.O. Box 940

Livingston, LA 70754

Phone 225-686-3100

Fax 225-686-7189

http://www.ligo.caltech.edu/

#### 1 Overview

This document shows proposed timing diagrams to communicate with the converters in the fast digital servo board. The main clock is assumed to be  $2^{28}$  Hz (or roughly 268 MHz), which is derived from the  $2^{26}$  Hz timing clock through the help of a PLL.

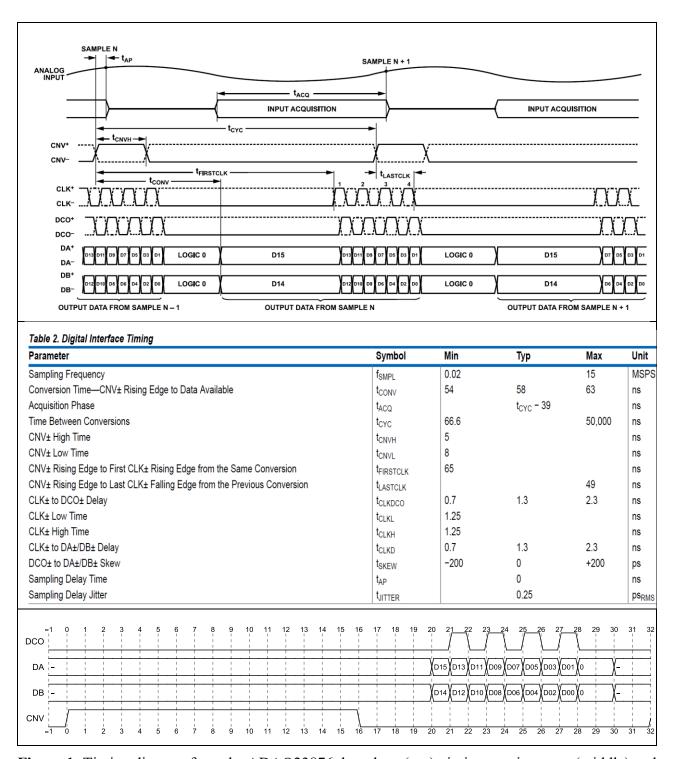

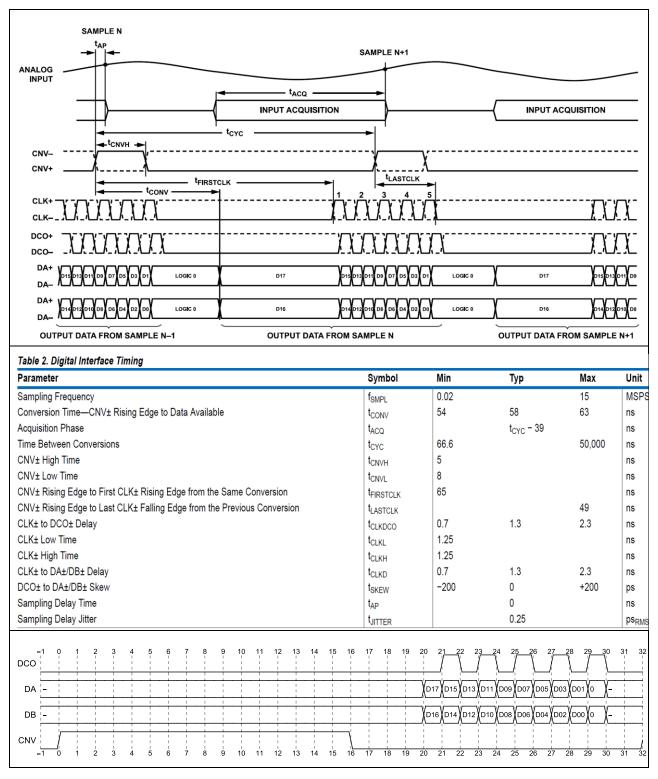

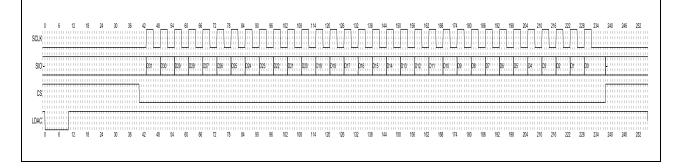

## 2 ADAQ23876 and ADAQ23878 ADCs

These ADCs have an LVDS interface that can be clocked at rates up to 400 MHz. Since we are using two lanes to transfer the data a 134MHz clock frequency is sufficient.

See Figure 1 for the ADAQ23876, and figure 2 for the ADAQ23878.

A full conversion plus readout takes 32 cycles and supports a 2<sup>23</sup> Hz (8.4 MHz) conversion clock.

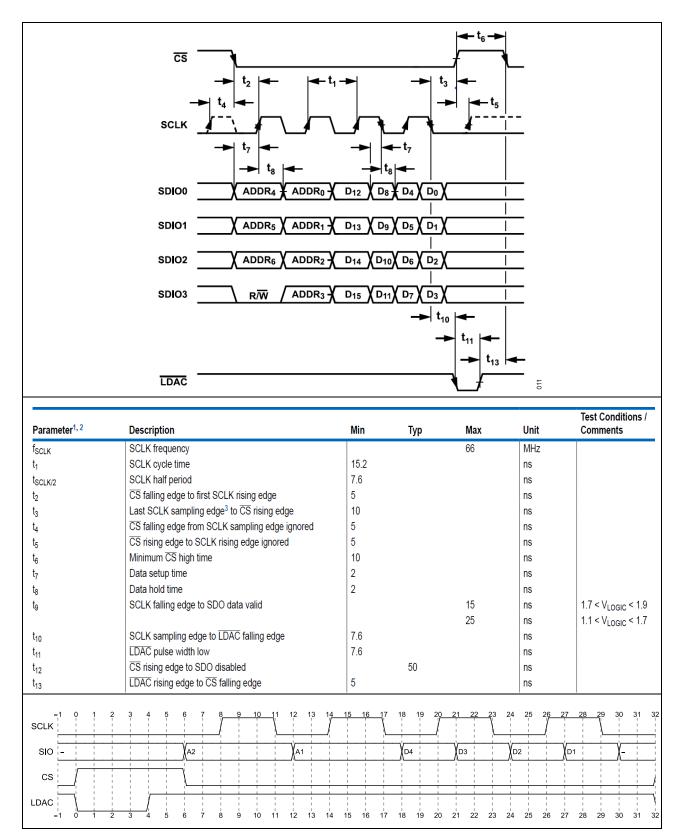

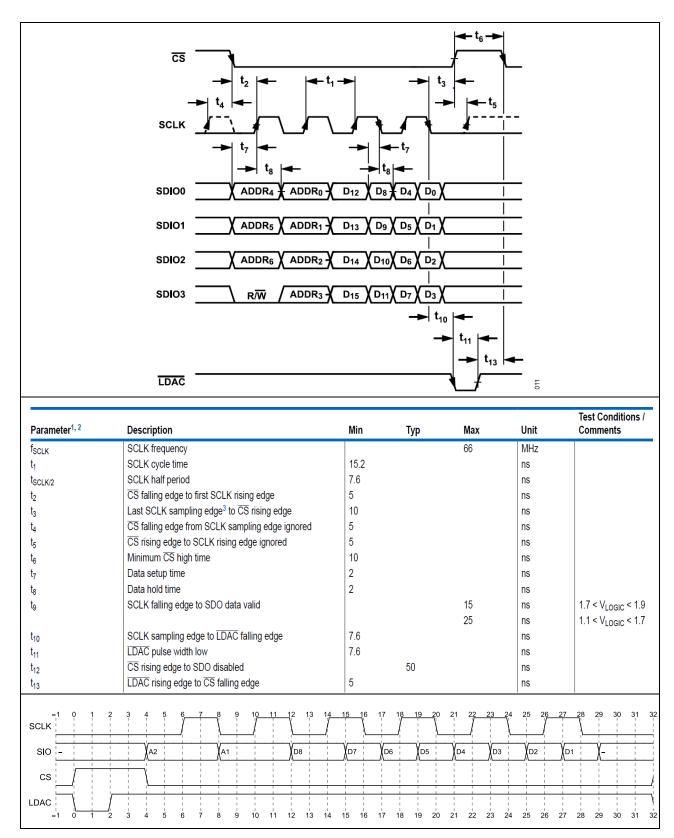

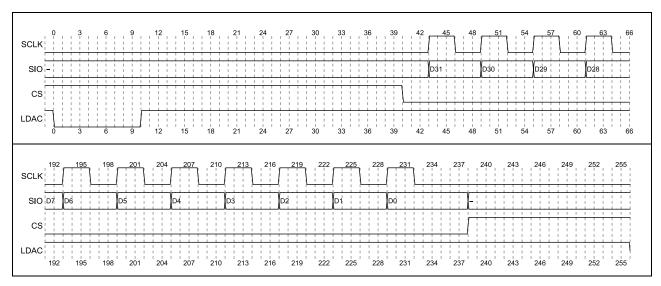

## 3 AD3551R and AD3552R

These DACs have quad SPI interface that can be clocked at rates up to 66 MHz. This is slightly lower than a 2<sup>26</sup> Hz (67.1 MHz) clock, which means that we cannot easily support the AD3552R in a non-streaming mode unless we run the interface 1.6% faster than recommended. For the AD3551R we can use 6 clock cycles at 268 MHz for one SPI clock cycle which results in a 44.7 MHz SPI clock.

See Figure 3 for the AD3551R, and figure 4 for the AD3552R.

A full conversion plus readout takes 32 cycles and supports a 2<sup>23</sup> Hz (8.4 MHz) conversion clock when the AD3552R is operated at 67.1 MHz. In principle, it is possible to run these devices in streaming mode that does not require a full address/data cycle but instead keeps sending the data only. This would allow the AD3552R to meet the timing requirements but could result in prolonged invalid data outputs if a SPI cycle is ever missed.

#### 4 DAC11001B

These DACs have SPI interface that can be clocked at rates up to 50 MHz assuming DV<sub>DD</sub> is 5V and IOV<sub>DD</sub> is 3.3V. Since 32 bits need to be transmitted per conversion cycle, we can support a  $2^{20}$  Hz (1 MHz) sampling clock for the precision DAC.

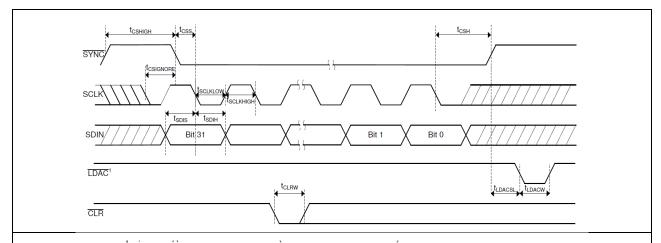

See Figure 5 for the DAC11001B timing diagram.

We again use 6 clock cycles at 268 MHz for one SPI clock cycle resulting in a 44.7 MHz SPI clock. Since this interface is single lane, without DDR and requires 32-bits per cycle, we can support a  $2^{20}$  Hz (1 MHz) sampling clock. With a reduced IOV<sub>DD</sub> at 2.5V or 1.8V we would have to half the sampling clock.

**Figure 1:** Timing diagram from the ADAQ23876 data sheet (top), timing requirements (middle) and proposed FPGA timing.

**Figure 2:** Timing diagram from the ADAQ23878 data sheet (top), timing requirements (middle) and proposed FPGA timing.

**Figure 3:** Timing diagram from the AD3551R data sheet (top), timing requirements (middle) and proposed FPGA timing.

**Figure 4:** Timing diagram from the AD3552R data sheet (top), timing requirements (middle) and proposed FPGA timing. Notice the slight timing violation.

|                       |                                                                                                | MIN | NOM | MAX | UNIT  |

|-----------------------|------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| f <sub>SCLK</sub>     | SCLK frequency, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                              |     |     | 33  | MHz   |

|                       | SCLK frequency, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                              |     |     | 50  | IVIHZ |

| <sup>t</sup> sclkHigh | SCLK high time, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                              | 15  |     |     | ns    |

|                       | SCLK high time, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                              | 10  |     |     |       |

| t <sub>sclkLow</sub>  | SCLK low time, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                               | 15  |     |     | no    |

|                       | SCLK low time, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                               | 10  |     |     | ns    |

| t <sub>SDIS</sub>     | SDI setup, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                   | 13  |     |     | ns    |

|                       | SDI setup, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                                   | 8   |     |     |       |

| t <sub>SDIH</sub>     | SDI hold, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                    | 13  |     |     | ns    |

|                       | SDI hold, $2.7 \text{ V} \leq \text{IOV}_{\text{DD}} \leq 5.5 \text{ V}$                       | 8   |     |     |       |

| t <sub>css</sub>      | SYNC falling edge to SCLK falling edge, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                      | 23  |     |     | ns    |

|                       | SYNC falling edge to SCLK falling edge, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                      | 18  |     |     |       |

| t <sub>сsн</sub>      | SCLK falling edge to \$\overline{\text{SYNC}}\$ rising edge, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V | 15  |     |     |       |

|                       | SCLK falling edge to \$\overline{\text{SYNC}}\$ rising edge, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V | 10  |     |     | ns    |

| t <sub>сsні</sub> дн  | SYNC high time, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                              | 55  |     |     | no    |

|                       | SYNC high time, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                              | 50  |     |     | ns    |

| t <sub>CSIGNORE</sub> | SCLK falling edge to SYNC ignore, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                            | 10  |     |     | no    |

|                       | SCLK falling edge to SYNC ignore, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                            | 5   |     |     | ns    |

| t <sub>LDACSL</sub>   | Synchronous update:  SYNC rising edge to LDAC falling edge, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V  | 50  |     |     |       |

|                       | Synchronous update:  SYNC rising edge to LDAC falling edge, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V  | 50  |     |     | ns    |

| t <sub>LDACW</sub>    | LDAC low time, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                               | 20  |     |     |       |

|                       | LDAC low time, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                               | 20  |     |     | ns    |

| t <sub>CLRW</sub>     | CLR low time, 1.7 V ≤ IOV <sub>DD</sub> < 2.7 V                                                | 20  |     |     | ns    |

|                       | CLR low time, 2.7 V ≤ IOV <sub>DD</sub> ≤ 5.5 V                                                | 20  |     |     |       |

|                       |                                                                                                |     |     |     |       |

**Figure 5:** Timing diagram from the DAC11001B data sheet (top), timing requirements (second) and proposed FPGA timing (full acquisition cycle, zoomed in at start of acquisition cycle and end of acquisition cycle).